# 基于 FPGA 的 CY7B923/933 复用解复用器在光纤通信中的应用

# 北京锦坤科技有限公司 www.jonkon.com.cn

高进,谢艳,覃宗厚(中国电子科技集团公司第三十四研究所,广西桂林 541004)

摘要:介绍一种 cypres s 公司的高速串行收发器 HOTLink CY7B923/933 的原理及其通过可编程器件 FPGA 实现 CY7B923/933 的光纤通信传输,给出了其系统设计原理简图。该收发器妁传输码率范围 160-400Mb/s,且功耗小,驱动能力强,有较强的鑫动查错功能,特别适用于光纤通信。

关键词: **复<u>用解复用器</u>**; 收发器; 光纤通信; FPGA

中阔分类号: TN929. 11 文献标志码: A

## 1 引 1 言

Cypress 公司的 HOTLink CY7B923 发送器和 CY7B933 接收器是专为点到点串行高速通信而设计的。它适用于光纤、同轴电缆以及双绞线作为通信介质,其传输码率范围为 160-400Mb/s: 可以自动进行 8B/IOB编解码,编码遵循 X3.230 协议,与光纤通信和 ESCON 协议兼容: HOTLink 收发器功耗较小(发送器 350mW,接收器 650mW),驱动能力很强。在不加任何补尝电路情况下,330Mb/s,对 50Ω 同轴电缆 (RG2582A/U)可以传送 35m,对 75Ω 同轴电缆(RG262A/U)可达 150m。若加上光电转换器用光纤传输.则可传输数十千米以上或更远的距离。笔者已经成功地通过 FPGA 控制实现将 CY7B923/933 应用于高速光 纡通信系统。下面将简要介绍收发器的原理。并重点介绍如何运用 FPGA 控制其在光纤通信中实际应用。

## 2、CY7B923/933 原理简介

# 2.1 CY7B923 发送器

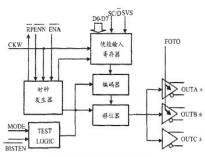

CY7B923 发送器有时钟产生器、使能输入寄存器、编码器、移位器及自检测试逻辑等主要功能模块组成.结构糕图如图 I 所示。CY78923 发送器将要发送的并行 8bit 数据锁存到内部寄存器后,编码器进行 8B/IOB编码.再由移位器移位串行输国,串行输出波特率是并行字节频率的 10 倍。同时有三路串行输出(OUTA±,OUTB±.OUTC±),均是差分 PECL 信号,其中 OUTA±,OUTB±.可由 FOTO 控制置成逻辑零而关闭光纤模块的光输出,OUTC±则不受控划。8B/10B编码也可以被关闭.而采用片外已经编码的 l0bit 数据(f旁通模式),可由 MODE 片脚控制(本文只介绍 8B/10B转换模式)8B/IOB编码。其它片脚简介如下:CKWf输入).数据写入时钟:D0-D7,并行输入数据:SC/D(输入),特殊字符或数据选择:ENA(输入),并行数据使能,在 CKW 的上跳沿。若 ENA 为低电平.则 D0~D7被锁存进内部输入寄存器进两被编码、发送:ENNf输入),下一个并行数据使能。若 ENN 为低电平,则在 CKW 的下一个上跳沿对的数据 D0-D7被锁存、编码、发送:BISTEN(f输入),内部自检使能:SVS(输入),故意产生一个发送错误:RP(输出),读脉冲,这是一个占空耽为 60%的、与 CKW 频率一致的读信号。

图 1 CY7B923 发送器结构框图

## 2.2 CY7B933 接收器

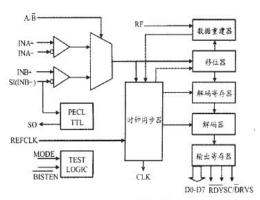

CY7B933 接收器主要功能模块有:时钟同步器、数据重建器、移位器、解码寄存器、解码器、输出寄存器及自检测试逻辑等。结构框图如图 2 所示。接收器有两路差分 PECL 信号(INA±, INB±)输入,可由 A/B 选其一。时钟同步器是由内部锁相环来保持与接收到的位流(bit stream)频率一致的,提供内部移位和解码时钟。数据重建器。若在接收到的位流中检测到同步码(K28.5),则复位内部位计数器。从而开始同步接收数据.为了防止干扰可由 RF 输入来使数据重建器停止工作.

图 2 CY7B933 接收器结构框图

CY78933 接收器与发送器一样也有两种工作模式.即编码模式和旁通模式(本文只介绍 8B/10B 编码模式)。这也是 MODE 片选引脚信号来选择。其它引脚简介如下: REF2CL K(输入),参考时钟; Q0-Q7,并行输出数据; SC/D(输出),特殊字符或数据指示,与发送器相似; RVS(输出),接收出错指示; RDY(输出),数据输出准备; CKR(输出),读出数据同步时钟,Q0-Q7、SC/D、RDY、RVS 都与 CKR 上升沿同步; SI(输入),既可以作为 INB 一,也可以是状态输入(PECL 信号): SOf 输出),状态输出,即是将 SI 信号的 PECL 电平转换成 TTL 电平输出; BISTEN(输入),内部自检使能控制。

## 3 系统设计及框图

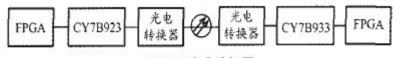

基于 FPGA 的 CY7B923 / 933 <u>复用 / 解复用器</u>的光纤通信系统应用由光发射端和光接收端组成. 系统设计框图如图 3 所示。

图 3 系统设计框图

CY78923 / 933 <u>复用 / 解复用器</u>用于光纤通信系统中(没用 FPGA). 笔者在试验中发现对数据不加任何控制处理时,光接收端 CY7B933 经常出现失锁. 不利于光纤通信:单独对光发射端的引脚如 ENA 进行控制时,先加电光接收端. 后加电光发射端时,CY7B933 锁定,系统正常工作: 但先加电光发射端,后加电光接收端时,CY7B933 失锁,系统工作不正常,这也不利于光纤通信。基于 FPGA 的 CY7B923 / 933 <u>复</u>用 / 解复用器的光纤通信系统应用能够更好地解决以上问题。

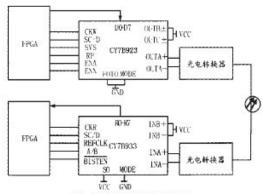

## 3. 1 光发射端

为了灵活运用 CY7B923 / 933. 本次系统设计时将 CY7B923 / 933 的所有输入、输出控制引脚和输入输出数据全部引入可编程 FPGA 中进行统一控制。本系统的设计关键在于如何保持光发射端与光接收端链路的稳定同步。为了使光接收端能时刻保持与发送端同步。系统对所有的数据输入重新编码。在数据

每一位的前半周期插入同步码型. 光接收端时刻先检测到同步码. 这样就不用担心整个系统光发射端和光接收端的加电先后顺序问题. 链路将时刻保持锁定正常状态。由于 CY7B923 选用 8B / 10B 编码模式. MODE 接地。不用的差分串行输出端 OUTB±、OUTC±接高电平。

#### 3. 2 光接收端

光接收端经过光电转换器恢复差分串行信号. 通过 CY7b933 把差分串行信号 INA±串并转换成 8 路并行输出信号 R0 一 R7。由于光发射端通过 FPGA 把输入的信号重新编码. 因此光接收端把输出的 8 路并行信号 R0 一 R7 送到可编程 FPGA 中解码还原出原始信号。

### 4 光纤通信系统中的应用实例

笔者已成功地将 HOTLink 收发器应用于一高速光纤通信系统。光发送端数据 D0 一 D7 从 FPGA 送出。 光接收端将收到的数据写入 FPGA。FPGA 选用 XINLINX9572. 经过 FPGA 对接收到的 R0 一 R7 重新处理还原出原始数据。系统设计原理简图如图 4 所示。本系统选用飞通 PT731I 一 41—1 光电转换器.供电电压+5V。当然,根据不通的传输距离应选用不同类型的光电转换器。

图 4 系统设计原理简图

## 5 结束语

从以上分析及应用电路可以看出。本系统为 HOTLinkCY7B923 / 933 高速收发器应于高速光纤通信提供了一个重要解决方案. 也为其他高速收发器器件应用于光纤通信提供了设计参考。

## 参考文献:

## [1]CYPILESS HOTLink Transmme"Receiver Datasheet.

[2]曾繁泰,陈美金,著. VHDL程序设计[M]. 北京:清华大学出版社,2001.

[3]吴冠华,王诚,编著. Altem FOGA, CPLD 设计[M]. 北京: 人民邮电出版社. 2005. 7.

北京锦坤科技有限公司 www.jonkon.com.cn